la interfaz SPI proporciona un método alternativo de comunicación con los µINS, µAHRS y µIMU. El protocolo SPI utiliza gran parte de la misma estructura y formato que el protocolo binario de comunicación en serie que se describe en la sección de protocolo binario del manual del usuario.

habilitar SPI¶

para habilitar SPI, Mantenga presionado el pin G9 (nSPI_EN) bajo al inicio.

Nota: Cuando la señal GPS PPS timepulse externa está habilitada en G9, el módulo ignorará la señal nSPI_EN y el modo SPI se desactivará independientemente del estado del pin G9.,

Hardware¶

La interfaz inercial Sense SPI utiliza 5 líneas para interactuar con otros dispositivos., id=»c075f8374e»>

Data Transfer¶

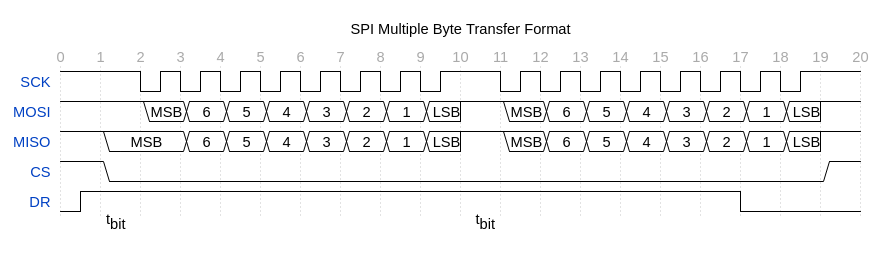

para garantizar el correcto comportamiento del receptor en modo esclavo SPI, el dispositivo maestro que envía el fotograma debe garantizar un retardo mínimo de un tbit (Tbit es el tiempo nominal requerido para transmitir un bit) entre cada transmisión de caracteres., Los dispositivos de detección de inercia no requieren un borde descendente para iniciar una recepción de caracteres, sino solo un nivel bajo. Sin embargo, este nivel bajo debe estar presente en al menos un tbit antes del primer ciclo de reloj serie correspondiente al bit MSB. (1)

al leer los uINS y no hay datos listos, enviará ceros para los datos.

mantener el CS bajo no debería causar ningún problema. Sin embargo, si la sincronización entre los procesadores maestro y esclavo sale de sincronización, no hay nada que los vuelva a sincronizar., El rebote o ruido del suelo durante una transición podría causar que el uINS vea dos bordes del reloj cuando solo debería haber habido uno (debido a un ESD o un evento transitorio rápido). Subir y bajar la línea CS restablece el registro de cambios resincronizará los relojes.

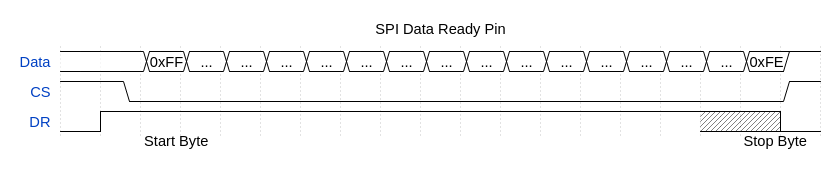

opción de Pin listo para datos¶

hay una opción de pin listo para datos. Esta señal se elevará cuando los datos estén listos. Dependiendo de cuando esto suceda, puede haber 1-4 bytes de ceros que saldrán antes de que comience el paquete. También esta línea irá inactiva un byte o dos antes de que el final del paquete sea enviado., No hay un carácter» no en un paquete de datos » para enviar. Se hace estrictamente por PIN listo de datos y análisis.

si la línea de selección de chip se baja durante un paquete de datos, el byte que se transmite (o que se transmitiría) se puede perder. Se recomienda bajar solo el chip select cuando está fuera de un paquete de datos y el pin listo para datos está inactivo.

el búfer interno SPI es de 4096 bytes. Si hay un desbordamiento de búfer, el búfer se cae. Esto se indica mediante un pin listo para datos que es alto sin que los datos estén allí., Cuando ocurre un desbordamiento, borra el búfer, por lo que el sistema podría estar en medio de un paquete y los uINS simplemente enviarían ceros. Si se envía una solicitud a los uINS o los uINS envían un paquete periódicamente, se resolverá la situación.

la interfaz SPI admite una velocidad de datos de hasta 3 Mbs. (5 Mbs funciona si el pin listo para datos se utiliza para recibir los datos-Ver B abajo.)

lectura de datos¶

hay dos estrategias que se pueden utilizar para leer los datos:

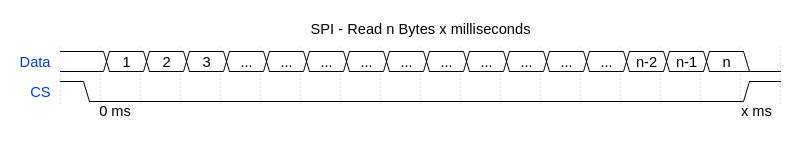

A. leer un tamaño de datos fijo cada intervalo de tiempo establecido., Se leerán más datos de los que el uINx producirá en un intervalo regular, por ejemplo, leyendo 512 bytes cada 4 ms.

el paquete será rellenado 0x00 si los bytes leídos exceden el tamaño del paquete.

el paquete será rellenado 0x00 si los bytes leídos exceden el tamaño del paquete.

B. lea mientras el pin listo para datos está activo o estamos dentro de un paquete de datos. Una anomalía es que el pin listo para datos caerá un byte o dos antes de que el final se bloquee, por lo tanto, es necesario vigilar el final del paquete.

Pseudo código para la lectura de datos:¶

- Check data ready pin. Si el pin es bajo, retarde y verifique el pin nuevamente.,

- baje la línea CS y lea un bloque de datos. Los tamaños de lectura son arbitrarios, pero tiende a funcionar mejor si el recuento de lectura es lo suficientemente largo como para contener la mayoría de los paquetes de datos.

- Después de completar la lectura, verifique el pin listo para datos. Si es alta, lea más datos. No levante la línea CS mientras el pin listo para datos es alto, causará pérdida de datos. Si data ready es bajo, levante la línea CS. En un sistema ocupado (y dependiendo de la velocidad en baudios) esto tendría que suceder junto con los datos leídos, ya que el pin listo para datos podría no bajar entre paquetes.,

- Analizar datos Buscando el inicio del paquete (0xFF) descartando datos hasta que se encuentren. Una vez encontrado empezar a guardar los datos.

- guardar y analizar datos Buscando el fin del paquete (0xFE). Una vez encontrado enviar el paquete para su uso. Si se ve un carácter de inicio de paquete mientras se busca el final, deseche los datos anteriores y comience a guardar el paquete.

EVB-2 SPI Dev Kit¶

El EVB-2 muestra la interfaz SPI con los uINS. El procesador EVB-2 ATSAM-E70 (E70) proporciona la interfaz SPI de ejemplo con los uINS., El EVB-2 debe ponerse en modo CBPreset 6 (CONFIG led color cyan) seguido de un reinicio del sistema para habilitar el modo SPI. El código fuente del proyecto EVB-2 (E70) está disponible en el SDK para referencia.

solución de problemas¶

Si todos los demás caracteres de un paquete se pierden, puede ser que la línea CS se esté alternando después de cada byte.

el uINS 3.1 utiliza un periférico USART SPI que requiere un retardo mínimo de un Tbit (tbit es el tiempo nominal requerido para transmitir un bit) entre los caracteres enviados. La lectura de bytes uno por uno puede causar retrasos de tiempo significativos al transmitir datos., Dependiendo de la cantidad de transmisión de datos, el uINS mable para mantenerse al día y el búfer podría desbordarse. Las solicitudes de un solo mensaje deberían funcionar correctamente, pero la transmisión probablemente no funcionará bien. Si el hardware maestro no puede manejar el retraso, se debe usar el hardware uINS 3.2.