SPI 인터페이스는 대체 방법을 제공합 통신 µINS,µAHRS 및 µIMU. SPI 프로토콜은 사용자 설명서의 이진 프로토콜 섹션에 설명 된 직렬 통신 이진 프로토콜과 동일한 구조 및 형식을 많이 사용합니다.

Spi 활성화¶

SPI 를 활성화하려면 시작시 핀 G9(nSPI_EN)를 낮게 잡으십시오.

참고:외부 GPS PPS timepulse 신호가 활성화에 G9,모듈을 무시하 nSPI_EN 신호 및 SPI 사이의 G9 핀 상태입니다.,

하드웨어¶

관성 감각 SPI 인터페이스는 다른 장치와 인터페이스하기 위해 5 라인을 사용합니다., id=”c075f8374e”>

데이터 전송¶

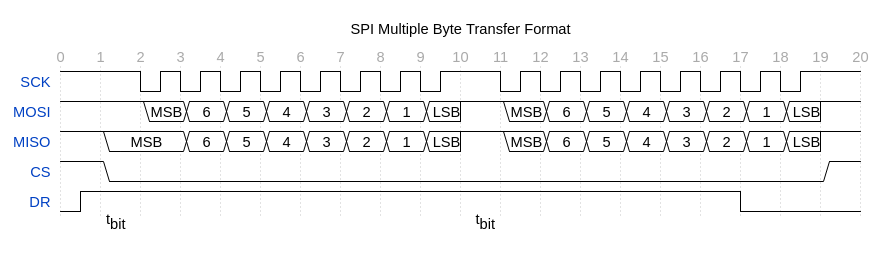

올바른 동작을 보장하려면 수신기의 SPI 슬레이브 모드 마스터를 보내는 장치 프레임지 확인해야 합 최소 지연의 tbit(tbit 는 명목하는 데 필요한 시간을 전송 비트)사이의 각 문자를 전송합니다., 관성 감지 장치는 문자 수신을 시작하기 위해 떨어지는 가장자리가 필요하지 않지만 낮은 수준 만 필요합니다. 그러나,이 낮은 레벨은 MSB 비트에 대응하는 제 1 직렬 클록 사이클 전에 적어도 하나의 tbit 상에 존재해야 한다. (1)

을 읽을 때 uINS 과 데이터 준비를 보낼 것입니다 제로에 대한 데이터이다.

CS 를 낮게 유지하면 문제가 발생하지 않아야합니다. 그러나 마스터 프로세서와 슬레이브 프로세서 간의 클럭킹이 동기화되지 않으면 다시 동기화 할 수있는 것이 없습니다., 지상 반송하거나 소환 중에 발생할 수 있습 uINS 보는 두 개의 가장자리에 시계가 있을 때가 있어야만 하나의(인 ESD 또는 고속 과도 응답 가능) CS 라인 재설정을 올리거나 내리면 시프트 레지스터가 클럭을 다시 동기화합니다.

데이터 준비 핀 옵션¶

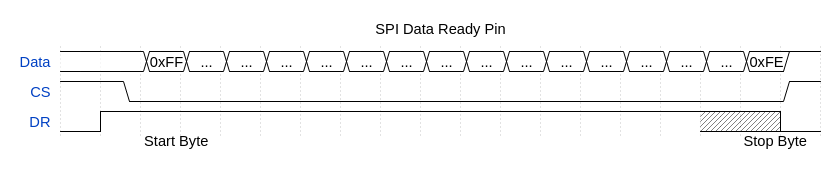

데이터 준비 핀 옵션이 있습니다. 이 신호는 데이터가 준비 될 때 발생합니다. 이런 일이 발생하는시기에 따라 패킷이 시작되기 전에 나올 1-4 바이트의 0 이있을 수 있습니다. 또한이 줄은 패킷의 끝이 전송되기 전에 바이트 또는 두 개의 비활성 상태로 이동합니다., 보낼”데이터 패킷에 없음”문자가 없습니다. 데이터 준비 핀 및 구문 분석에 의해 엄격하게 수행됩니다.

데이터 패킷 중에 칩 선택 라인이 낮아지면 전송되는 바이트(또는 전송되는 바이트)가 손실 될 수 있습니다. 데이터 패킷 외부와 데이터 준비 핀이 비활성 상태일 때만 칩 선택을 낮추는 것이 좋습니다.

내부 SPI 버퍼는 4096 바이트입니다. 버퍼 오버플로가 있으면 버퍼가 삭제됩니다. 이는 데이터가 존재하지 않고 높은 데이터 준비 핀으로 표시됩니다., 오버플로가 발생하면 버퍼를 지우므로 시스템이 패킷의 중간에있을 수 있고 uINS 는 0 을 보내면됩니다. Uins 에 요청을 보내거나 uINS 가 패킷을 주기적으로 보내면 상황이 해결됩니다.

SPI 인터페이스는 최대 3Mbs 데이터 속도를 지원합니다. (5Mbs 는 데이터 준비 핀이 데이터를 수신하는 데 사용되는 경우 작동합니다-아래 B 를 참조하십시오.)

데이터를 읽¶

두 가지 전략을 사용할 수 있는 데이터를 읽:

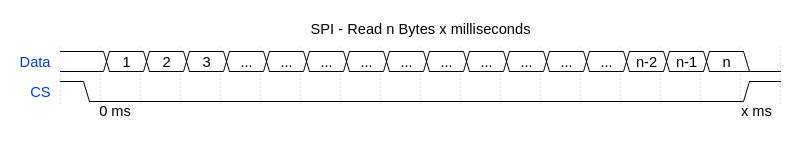

A. 읽 고정 데이터 크기의 모든 설정된 시간 간격입니다., 더 많은 데이터를 읽을 수 있다 uINx 생산에 일정 간격,예를 들어,읽기 512 개의 바이트는 모든 4ms.

패킷을 것입 0x00 패딩면 읽은 바이트를 초과하는 패킷 크기입니다.

패킷을 것입 0x00 패딩면 읽은 바이트를 초과하는 패킷 크기입니다.

B. 데이터 준비 핀이 활성 상태이거나 데이터 패킷 내부에있는 동안 읽습니다. 중 하나 이상의 데이터 준비 pin 도가 바이트 또는 두 개의 끝나기 전에 가져오는 클럭으로,따라서 필요로하는계의 종료에 대한 패킷을 전송합니다.

데이터를 읽는 의사 코드:¶

- 데이터 준비 핀을 확인하십시오. 핀이 낮 으면 지연하고 핀을 다시 확인하십시오.,

- Cs 라인을 낮추고 데이터 블록을 읽습니다. 읽기 크기는 임의적이지만 읽기 횟수가 대부분의 데이터 패킷을 포함 할만큼 충분히 길면 더 잘 작동하는 경향이 있습니다.

- 읽기가 완료되면 데이터 준비 핀을 확인하십시오. 그것이 높으면 더 많은 데이터를 읽으십시오. 데이터 준비 핀이 높은 동안 CS 라인을 제기하지 마십시오,그것은 데이터 손실의 원인이됩니다. 데이터 준비가 낮 으면 CS 라인을 올리십시오. 에서 바쁜 시스템(과에 따라 전송 속도)이 필요로 하는 일이와 함께 데이터를 읽으로 데이터 준비 pin 지 않을 수도 있습 낮은 이동에 사 패킷입니다.,

- 찾을 때까지 데이터를 폐기하는 패킷(0xFF)시작을 찾는 데이터를 구문 분석합니다. 일단 발견되면 데이터 저장을 시작하십시오.

- 패킷 끝(0xFE)을 찾는 데이터를 저장하고 구문 분석합니다. 일단 사용을 위해 패킷을 보내 발견. 끝을 찾는 동안 패킷 문자의 시작이 보이면 이전 데이터를 버리고 패킷 저장을 시작하십시오.

EVB-2SPI Dev Kit¶

EVB-2 는 uINS 와의 SPI 인터페이스를 보여줍니다. EVB-2ATSAM-E70(E70)프로세서는 uINS 와 예제 SPI 인터페이스를 제공합니다., EVB-2 는 CBPreset 모드 6(CONFIG led 컬러 시안 색)에 넣어야하며 spi 모드를 활성화하기 위해 시스템을 재설정해야합니다. EVB-2(E70)프로젝트 소스 코드는 참조 용으로 SDK 에서 사용할 수 있습니다.

문제를 해결¶

경우 다른 모든 문자에서 패킷을 잃었습니다 수 있습 CS 되고 있는 전환 후에는 모든 바이트.

uINS3.1 사용 USART SPI peripherial 필요한 최소 지연의 tbit(tbit 는 명목하는 데 필요한 시간을 전송 비트)사이의 간격을 문자를 보냈습니다. 바이트를 하나씩 읽으면 데이터를 스트리밍 할 때 signifacnt 시간 지연이 발생할 수 있습니다., 데이터 스트리밍의 양에 따라 uins mable 이 유지되고 버퍼가 오버플로 될 수 있습니다. 단일 메시지 요청이 제대로 작동해야하지만 스트리밍은 아마도 잘 작동하지 않을 것입니다. 마스터 하드웨어가 지연을 처리 할 수없는 경우 uINS3.2 하드웨어를 사용해야합니다.