SPIインタフェースは、μin、μahrs、およびμimuとの通信の代替方法を提供します。 SPIプロトコルは、ユーザーマニュアルのバイナリプロトコルセクションで概説されているシリアル通信バイナリプロトコルと同じ構造と形式の多くを

SPIをイネーブル¶

SPIをイネーブルするには、起動時にピンG9(nSPI_EN)をロー-レベルに保ちます。注:g9で外部GPS PPS timepulse信号がイネーブルされている場合、モジュールはnSPI_EN信号を無視し、G9ピンの状態に関係なくSPIモードはディスエーブルされます。,

ハードウェア¶

慣性検出SPIインタフェースは、5ラインを使用して他のデバイスとインタフェースします。, id=”c075f8374e”>

データ転送¶

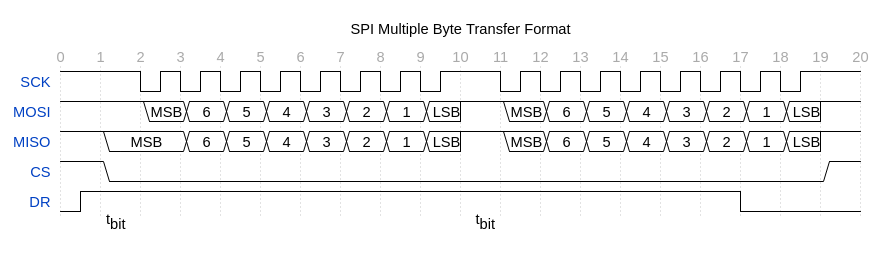

spiスレーブモードでレシーバの正しい動作を確保するためには、フレームを送信するマスタデバイスは、各文字伝送の間にtbit(tbitはビットを送信するのに必要な公称時間)の最小遅延を確保する必要があります。, 慣性感覚デバイスは、文字受信を開始するためにの立下がりエッジを必要とせず、低レベルのみを必要とする。 しかし、この低レベルに必ず含まれていなければならないの少なくとも一つのtbit前のシリアルクロックサイクルに対応するMSBます。 (1)

uinを読み取り、データの準備ができていないときは、データのゼロを送信します。

CSを低く保つことは問題を引き起こしてはなりません。 ただし、マスタープロセッサとスレーブプロセッサ間のクロックが同期しなくなった場合、同期に戻すものは何もありません。, 遷移中のグラウンドバウンスまたはノイズにより、ESDまたは高速トランジェントイベントにより、一つだけがあるはずのときにuinが二つのクロックエ CSラインを上げ下げすると、シフトレジスタはクロックを再ynchronします。

データレディピンオプション¶

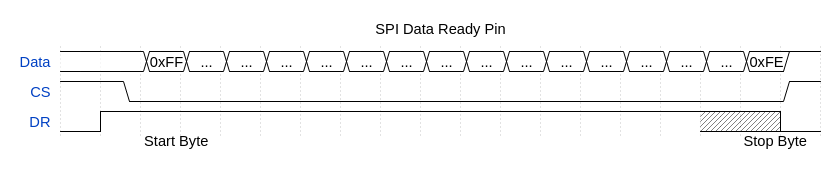

データレディピンオプションがあります。 この信号は、データの準備ができたときに発生します。 これがいつ起こるかによって包みが始まる前に出て来るゼロの1-4バイトがある場合もある。 また、この行はパケットの終わりが送信される前に非アクティブになります。, 送信する”not in a data packet”文字はありません。 それは厳密にデータ準備ピンと解析によって行われます。

データパケット中にチップセレクトラインが低下すると、送信されている(または送信されるであろう)バイトが失われる可能性があります。 データパケットの外側でdata readyピンが非アクティブな場合にのみ、チップセレクトを低くすることをお勧めします。

内部SPIバッファは4096バイトです。 がある場合はバッファオーバーフローのバッファーが落ちてしまいました。 これは、データが存在せずにハイであるデータレディピンによって示されます。, オーバーフローが発生すると、バッファがクリアされるため、システムはパケットの途中にあり、uinはゼロを送信するだけです。 要求がuINSに送信された場合、またはuINSが定期的にパケットを送信する場合、状況は解決されます。

SPIインタフェースは最大3Mbsのデータレートをサポートします。 (5Mbsは、データレディピンを使用してデータを受信する場合に機能します-以下のBを参照してください。)

データの読み取り¶

データの読み取りに使用できる二つの戦略があります。

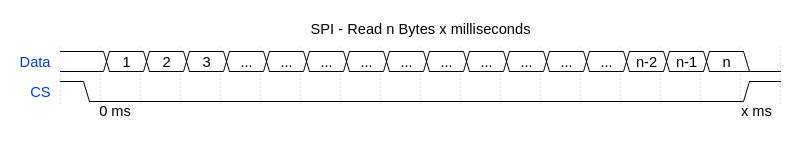

A.設定された時間間隔ごとに固定データサイズを読み取ります。, たとえば、512バイトを4ミリ秒ごとに読み取るなど、uinxが一定の間隔で生成するよりも多くのデータが読み取られます。

読み取られたバイトがパケットサイズを超える場合、パケットは0x00パディングされます。

読み取られたバイトがパケットサイズを超える場合、パケットは0x00パディングされます。

B.data readyピンがアクティブであるか、データパケット内にいる間に読み取ります。 一つの異常は、データレディピンが終了がクロックアウトされる前にバイトまたは二つをドロップするため、パケットの終了を監視する必要があるこ

データを読み取るための擬似コード:√

- データレディピンをチェックします。 Pinがlowの場合は、再度pinを遅らせてチェックしてください。,

- CS行を下げ、データブロックを読み取ります。 読みのサイズは任意のものになりがちなので良いと思われる場合、読み込み数が長いほどれもデータパケット.

- 読み出しが完了したら、data readyピンをチェックしてください。 高い場合は、より多くのデータを読み取ります。 Data readyピンがハイ-レベルの間はCSラインを上げないでください。 データレディがローの場合は、CSラインを上げます。 ビジーシステム(およびボーレートに応じて)では、data readyピンがパケット間でローにならない可能性があるため、これは読み取られたデータとともに発生する必,

- パケットの開始(0xFF)を探してデータを解析し、見つかるまでデータを破棄します。 一度データの保存を開始見つかりました。

- パケットの終わり(0xFE)を探してデータを保存して解析します。 また送信パケットがoffで使用するものです。 終わりを探している間にパケットの開始文字が見られた場合は、以前のデータを破棄し、パケットの保存を開始します。

EVB-2SPI Dev Kit¶

EVB-2は、uinとのSPIインタフェースを示しています。 EVB-2ATSAM-E70(E70)プロセッサは、uinとのSPIインタフェース例を提供します。, SPIモードをイネーブルにするには、EVB-2をCBPresetモード6(CONFIG led color cyan)にした後、システムリセットを行う必要があります。 EVB-2(E70)プロジェクトのソースコードは、参照用にSDKで入手できます。

トラブルシューティング¶

パケットの他のすべての文字が失われた場合、CS行がすべてのバイトの後に切り替えられている可能性があります。

uINS3.1はUSART SPIペリフェラルを使用しており、送信される文字間の間隔はtbit(tbitはビットを送信するのに必要な公称時間)の最小遅延を必要とします。 読書バイト一つ一つの原因となりsignifacnt時間の遅れがストリーミングデータです。, データストリーミングの量に応じて、uINSが追いつくことができ、バッファがオーバーフローする可能性があります。 単一のメッセージを要求すべき正常に動作し、ストリーミングも正しく設定してください マスターハードウェアが遅延を処理できない場合は、uINS3.2ハードウェアを使用する必要があります。